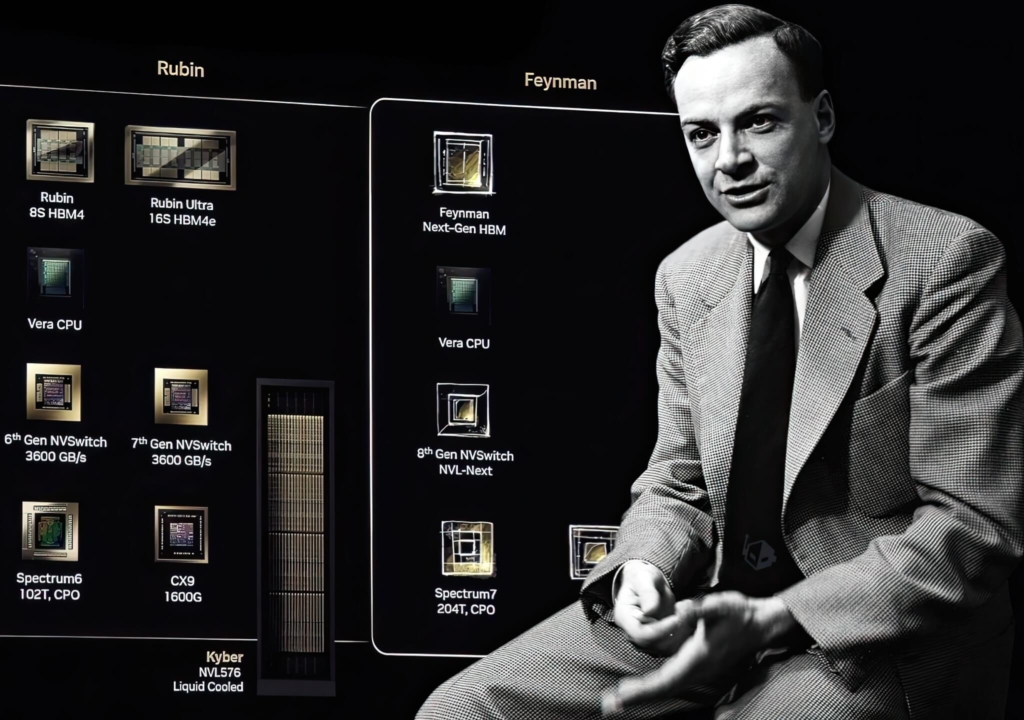

Nvidia đang vạch ra một kế hoạch đầy tham vọng nhằm thống trị hoàn toàn mảng suy luận (inference) trong lĩnh vực trí tuệ nhân tạo với thế hệ chip Feynman tiếp theo, dự kiến ra mắt vào năm 2028. Theo các phân tích chuyên sâu mới nhất, gã khổng lồ “đội Xanh” có thể sẽ tích hợp các đơn vị xử lý ngôn ngữ (LPU) của Groq trực tiếp vào kiến trúc của mình. Thay vì đặt chung trên một mặt phẳng, các đơn vị này nhiều khả năng sẽ được xếp chồng lên nhau dưới dạng các khuôn riêng biệt, một phương pháp gợi nhớ đến công nghệ X3D đầy thành công mà đối thủ AMD đang áp dụng.

Công nghệ xếp chồng chip và chiến lược suy luận AI của Nvidia

Thỏa thuận cấp phép sở hữu trí tuệ gần đây giữa Nvidia và Groq liên quan đến các đơn vị LPU thoạt nghe có vẻ chỉ là một bước phát triển khiêm tốn nếu chỉ nhìn vào quy mô mua lại hay các con số doanh thu bề nổi. Tuy nhiên, thực tế đằng sau cái bắt tay này là tham vọng to lớn của Nvidia nhằm vươn lên dẫn đầu trong phân khúc suy luận AI thông qua sức mạnh của LPU. Vấn đề được giới công nghệ quan tâm nhất hiện nay là Nvidia sẽ tích hợp công nghệ này như thế nào. Dựa trên nhận định của chuyên gia GPU AGF, có vẻ như các đơn vị LPU sẽ được xếp chồng lên các GPU Feynman thế hệ tiếp theo thông qua công nghệ liên kết lai (hybrid bonding) của TSMC.

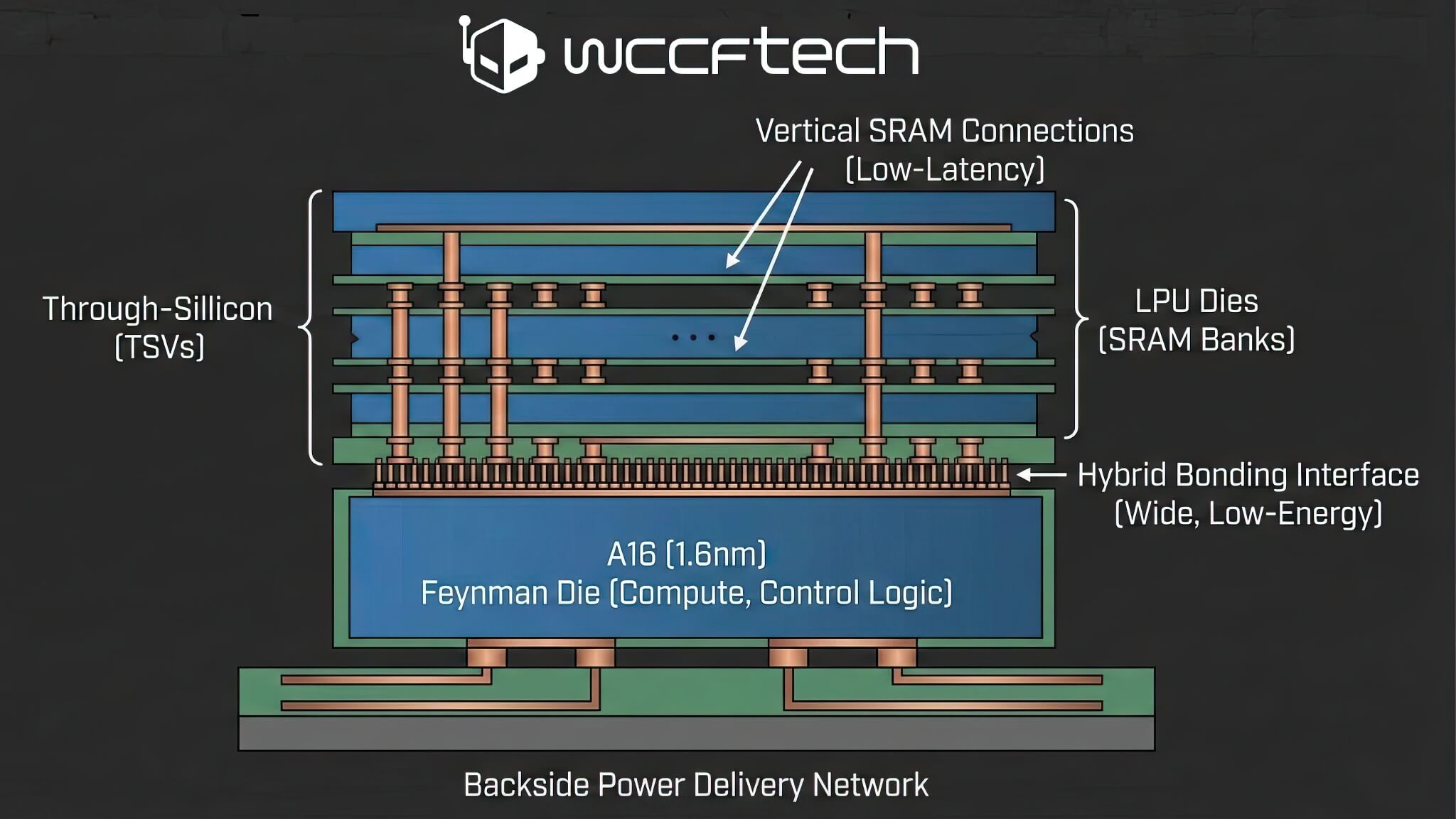

Vị chuyên gia này tin rằng việc triển khai thực tế có thể sẽ rất giống với những gì AMD đã làm với các dòng CPU X3D của họ. Cụ thể, AMD đã sử dụng công nghệ liên kết lai SoIC của TSMC để tích hợp các ô bộ nhớ đệm 3D V-Cache lên trên khuôn tính toán chính. AGF lập luận rằng việc tích hợp bộ nhớ SRAM dưới dạng một khuôn nguyên khối (monolithic) cùng với chip xử lý có thể không phải là nước đi đúng đắn cho GPU Feynman. Lý do là khả năng thu nhỏ kích thước của SRAM hiện đang gặp giới hạn vật lý, và việc cố gắng xây dựng nó trên các nút quy trình sản xuất tiên tiến sẽ dẫn đến lãng phí diện tích silicon cao cấp, từ đó làm tăng chi phí sử dụng trên mỗi đơn vị diện tích tấm wafer một cách đáng kể.

Thay vào đó, giải pháp hợp lý hơn là Nvidia sẽ xếp chồng các đơn vị LPU lên trên khuôn tính toán Feynman. Theo mô hình này, các chip sử dụng quy trình sản xuất A16 (1.6nm) sẽ đóng vai trò là khuôn Feynman chính, chứa các khối tính toán quan trọng như đơn vị tensor và logic điều khiển. Trong khi đó, các khuôn LPU riêng biệt sẽ chứa các ngân hàng bộ nhớ SRAM lớn. Để kết nối các thành phần này lại với nhau, công nghệ liên kết lai của TSMC sẽ đóng vai trò then chốt, cho phép tạo ra một giao diện kết nối rộng và tiêu tốn ít năng lượng hơn nhiều so với việc để bộ nhớ nằm rời rạc bên ngoài. Hơn nữa, vì quy trình A16 có tính năng cung cấp năng lượng từ mặt sau (backside power delivery), mặt trước của chip sẽ được giải phóng để dành cho các kết nối SRAM theo chiều dọc, đảm bảo phản hồi giải mã có độ trễ cực thấp.

Thách thức về nhiệt độ và tương thích phần mềm CUDA

Mặc dù ý tưởng về mặt kỹ thuật nghe rất hợp lý và hứa hẹn hiệu năng cao, nhưng phương pháp này cũng đặt ra không ít lo ngại, đặc biệt là về vấn đề quản lý nhiệt độ. Việc xếp chồng các khuôn chip lên nhau trên một quy trình hoạt động ở mật độ tính toán cao vốn dĩ đã là một thách thức lớn về tản nhiệt. Với các đơn vị LPU tập trung vào khả năng duy trì thông lượng dữ liệu liên tục, nhiệt lượng sinh ra có thể tạo ra các điểm nghẽn cổ chai về hiệu suất nếu không được xử lý tốt.

Quan trọng hơn, những tác động ở cấp độ thực thi phần mềm cũng sẽ gia tăng đáng kể với cách tiếp cận này. Các đơn vị LPU thường tập trung vào một thứ tự thực thi cố định, điều này tạo ra một sự xung đột tự nhiên giữa tính quyết định (determinism) và tính linh hoạt (flexibility) của hệ thống. Ngay cả khi Nvidia giải quyết được các ràng buộc về phần cứng, mối lo ngại chính vẫn nằm ở cách nền tảng phần mềm CUDA lừng danh của họ sẽ hoạt động như thế nào trong môi trường thực thi kiểu LPU.

Lý do là LPU yêu cầu việc sắp xếp bộ nhớ phải rõ ràng và cụ thể, trong khi các nhân CUDA lại được thiết kế theo hướng trừu tượng hóa phần cứng để dễ lập trình hơn. Việc tích hợp SRAM vào bên trong các kiến trúc AI theo cách này sẽ không phải là một nhiệm vụ dễ dàng đối với “đội Xanh”. Nó đòi hỏi một kỳ tích về mặt kỹ thuật để đảm bảo môi trường kết hợp giữa LPU và GPU được tối ưu hóa tốt nhất. Tuy nhiên, đây có thể là cái giá mà Nvidia sẵn sàng đánh đổi nếu họ thực sự muốn dẫn đầu và thống trị mảng suy luận trong kỷ nguyên AI sắp tới.