Microchip, nền tảng vi mô của điện toán, đang chạy đến giới hạn của vật lý, ngay khi nhu cầu AI và xử lý dữ liệu hiệu suất cao đạt đỉnh. Trong bối cảnh đó, các nhà nghiên cứu đang khám phá Wafer-Scale Integration (WSI) – một mô hình hoàn toàn mới sử dụng toàn bộ tấm wafer silicon làm một chất nền xử lý nguyên khối, thách thức giới hạn kích thước truyền thống và báo hiệu cho sự kết thúc của kỷ nguyên microchip hiện tại.

Giới hạn vật lý và sự phân mảnh của chip bán dẫn

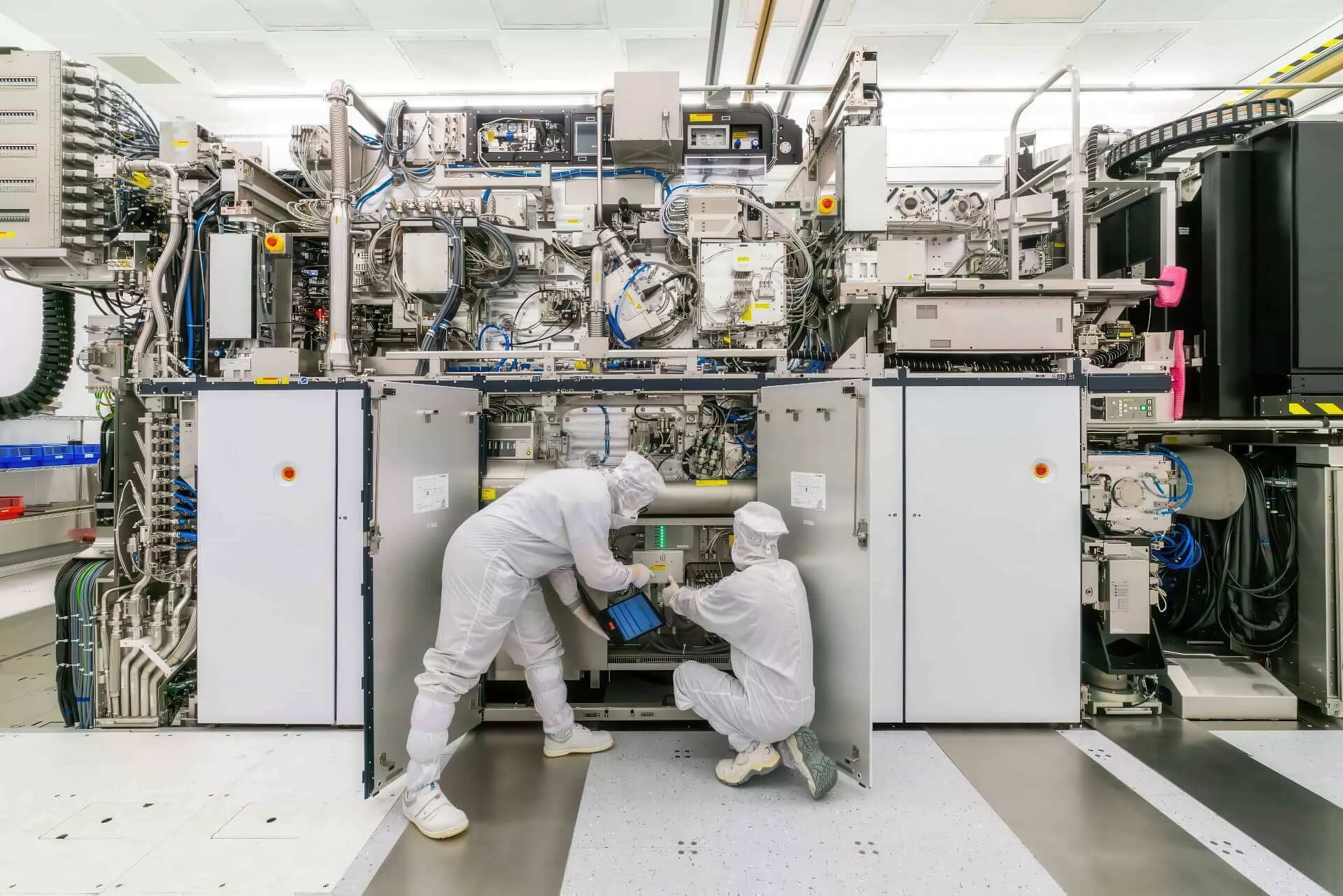

Nhu cầu tính toán cấp số nhân của AI đã dẫn đến một ngã rẽ bị chi phối bởi các quy luật vật lý bất biến. Cốt lõi của việc chế tạo chip là công nghệ quang khắc cực tím (extreme ultraviolet lithography – EUV), một quy trình bị thống trị bởi nhà sản xuất thiết bị Hà Lan ASML và cỗ máy “Extreme Machine” trị giá 380 triệu USD của họ. Công cụ này, trông giống một chiếc máy ảnh chuyên dụng cao cấp, chiếu sáng qua các mặt nạ quang học chính xác lên các tấm wafer silicon để định hình các mẫu mạch điện.

Mặc dù tinh vi, ngay cả hệ thống quang khắc tiên tiến nhất cũng phải đối mặt với một hạn chế cơ bản: giới hạn reticle. Quy luật vật lý này giới hạn kích thước của một khuôn chip đơn lẻ (single chip die) ở mức khoảng 800 mm vuông. Do đó, để đạt được khả năng xử lý lớn hơn, cần phải phân chia các nhiệm vụ máy tính trên nhiều chip nhỏ hơn (chiplets), được kết nối với nhau bằng các công nghệ đóng gói, cáp và liên kết sợi quang ngày càng dày đặc.

Những hạn chế kiến trúc này rất rõ ràng trong thiết kế đang phát triển của các trung tâm dữ liệu hiện đại, nơi xu hướng là hướng tới các “chiplets” nhỏ hơn được kết nối để mở rộng quy mô. Tuy nhiên, sự phân mảnh này lại làm tăng thêm chi phí giao tiếp, đòi hỏi những đổi mới đóng gói ngày càng thông minh, và làm tăng độ phức tạp của hệ thống.

Tương lai sau Microchip: Tích hợp Wafer-Scale và Công nghệ mới

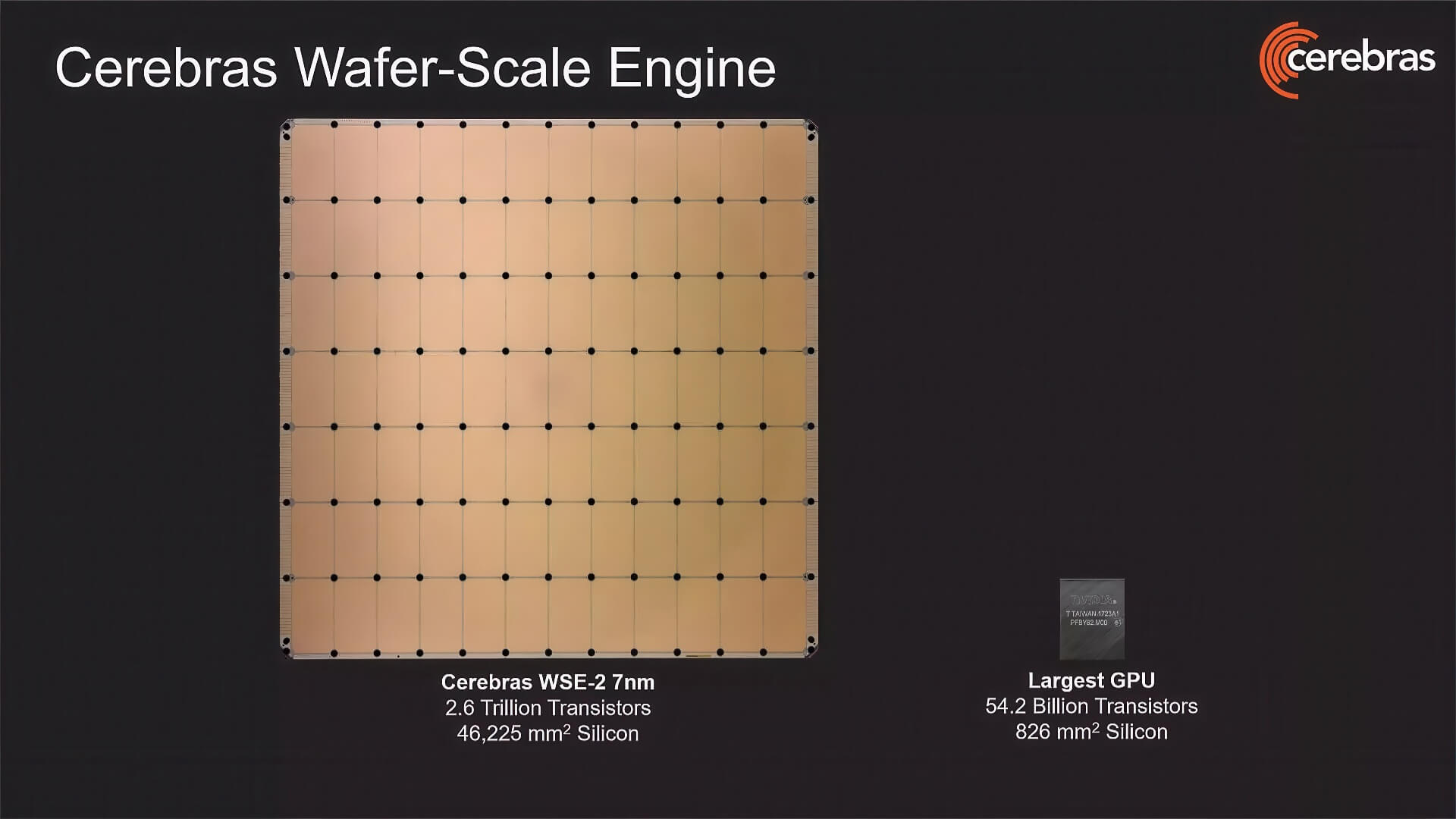

Đối mặt với cả giới hạn reticle và sự giảm dần lợi nhuận từ việc mở rộng quy mô gia tăng, các nhà nghiên cứu và công ty bán dẫn đang khám phá Tích hợp Wafer-Scale (Wafer-Scale Integration – WSI). Mô hình này từ bỏ hoàn toàn các chip rời rạc thông thường, thay vào đó sử dụng toàn bộ tấm wafer silicon làm một chất nền xử lý nguyên khối duy nhất.

Những nỗ lực gần đây của Cerebras, một công ty ở Palo Alto, đã mang lại WSE-3 (Wafer-Scale Engine 3). Chip này tích hợp bốn nghìn tỷ bóng bán dẫn và cung cấp băng thông bộ nhớ gấp 7.000 lần so với các chip thông thường hàng đầu. Không giống như các kiến trúc tiêu chuẩn, WSE-3 nhúng bộ nhớ trực tiếp vào trong wafer, giảm đáng kể độ trễ và thu nhỏ kích thước của toàn bộ trung tâm dữ liệu.

Tesla, dưới thời Elon Musk, đã thử nghiệm các khái niệm tương tự trong dự án Dojo của mình. Mặc dù đã bị ngừng phát triển nội bộ, cách tiếp cận này vẫn tồn tại trong các dự án mạo hiểm như DensityAI. Lam Research, một nhà cung cấp thiết bị chế tạo lớn, đã thúc đẩy công nghệ quang khắc chùm tia điện tử đa cột (multi-column electron-beam lithography) – thông qua công ty spinout là Multibeam Corp. – cung cấp cho các nhà sản xuất một con đường để khắc các tấm wafer lớn hơn nhiều, vượt qua rào cản reticle.

Những phát triển này cho thấy triều đại của microchip có thể sẽ sớm nhường chỗ cho các kiến trúc khác biệt đáng kể về cả hình thức và chức năng. Khi việc tích hợp wafer-scale và các kỹ thuật quang khắc mới trưởng thành, khả năng về “các trung tâm dữ liệu trong một hộp” (data centers-in-a-box) trở nên hữu hình, thách thức hiện trạng kinh tế và công nghệ đã thống trị cơ sở hạ tầng kỹ thuật số trong nhiều thế hệ.